## INTERNATIONAL **STANDARD**

## ISO/IEC/IEEE 8802-3

Second edition 2017-03-01

AMENDMENT 8 2018-100

Information technology — Sind Harrid 8.\*

Telecommunications are exchange between and me Telecommunications and information and metropolitan area networks — Specific requirements -

Part 3: Standard for Ethernet

AMENDMENT 8: Physical layer and management parameters for power over data lines (PoDL) of single balanced twisted-pair ethernet

STANDARDSISO. COM. Click to Vis Technologies de l'information — Télécommunications et échange d'information entre systèmes — Réseaux locaux et métropolitains — Prescriptions spécifiques —

Partie 3: Norme pour Ethernet AMENDEMENT 8: Titre manque

## COPYRIGHT PROTECTED DOCUMENT

All rights reserved. Unless otherwise specified, or required in the context of its implementation, no part of this publication may be reproduced or utilized otherwise in any form or by any means, electronic or mechanical, including photocopying, or posting on the internet or an intranet, without prior written permission. Permission can be requested from either ISO or IEEE at the respective address below or ISO's member body in the country of the requester.

ISO copyright office CP 401 • Ch. de Blandonnet 8 CH-1214 Vernier, Geneva Phone: +41 22 749 01 11 Fax: +41 22 749 09 47

Email: copyright@iso.org Website: www.iso.org Published in Switzerland

Institute of Electrical and Electronics Engineers, Inc 3 Park Avenue, New York NY 10016-5997, USA

Email: stds.ipr@ieee.org Website: www.ieee.org

#### Foreword

ISO (the International Organization for Standardization) and IEC (the International Electrotechnical Commission) form the specialized system for worldwide standardization. National bodies that are members of ISO or IEC participate in the development of International Standards through technical committees established by the respective organization to deal with particular fields of technical activity. ISO and IEC technical committees collaborate in fields of mutual interest. Other international organizations, governmental and non-governmental, in liaison with ISO and IEC, also take part in the work.

The procedures used to develop this document and those intended for its further maintenance are described in the ISO/IEC Directives, Part 1. In particular the different approval criteria needed for the different types of ISO documents should be noted (see <a href="https://www.iso.org/directives">www.iso.org/directives</a>).

IEEE Standards documents are developed within the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association (IEEE-SA) Standards Board. The IEEE develops its standards through a consensus development process, approved by the American National Standards Institute, which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of the Institute and serve without compensation. While the IEEE administers the process and establishes rules to promote fairness in the consensus development process, the IEEE does not independently evaluate, test, or verify the accuracy of any of the information contained in its standards.

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO and IEC shall not be held responsible for identifying any or all such patent rights. Details of any patent rights identified during the development of the document will be in the Introduction and/or on the ISO list of patent declarations received (see <a href="https://patents.iec.ch">www.iso.org/patents</a>) or the IEC list of patent declarations received (see <a href="https://patents.iec.ch">https://patents.iec.ch</a>).

Any trade name used in this document is information given for the convenience of users and does not constitute an endorsement.

For an explanation of the voluntary nature of standards, the meaning of ISO specific terms and expressions related to conformity assessment, as well as information about ISO's adherence to the World Trade Organization (WTO) principles in the Technical Barriers to Trade (TBT) see: www.iso.org/iso/foreword.html.

ISO/IEC/IEEE 8802-3:2017/Amd.8 was prepared by the LAN/MAN of the IEEE Computer Society (as IEEE Std 802.3bu-2016) and drafted in accordance with its editorial rules. It was adopted, under the "fast-track procedure" defined in the Partner Standards Development Organization cooperation agreement between ISO and IEEE, by Joint Technical Committee ISO/IEC JTC 1, Information technology, Subcommittee SC 6, Telecommunications and information exchange between systems.

A list of all parts in the ISO/IEC/IEEE 8802 series can be found on the ISO website.

Any feedback or questions on this document should be directed to the user's national standards body. A complete listing of these bodies can be found at <a href="https://www.iso.org/members.html">www.iso.org/members.html</a>.

STANDARDSEO, COM. Click to risw the full POF of SOURCE, REFE 8802.3.20 THAND STANDARDSEO, COM. Click to risw the full POF of SOURCE, REFE 8802.3.20 THAND STANDARDSEO, COM. Click to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, COM. Click to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, COM. Click to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, COM. Click to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, COM. Click to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, COM. CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, COM. CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, COM. CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, COM. CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, COM. CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, COM. CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, CLICK to risw the full POF of SOURCE, REFE 8802.3.20 THANDARDSEO, CLICK TO REFE 8802.3.20 THANDARDSEO,

J16

Jenent to

J2.3™-2015

Jas amended by

J802.3bv™-2015,

Std 802.3by™-2016,

JEE Std 802.3bp™-2016,

IEEE Std 802.3bp™-2016,

IEEE Std 802.3br™-2016,

IEEE Std 802.3br™-2016,

IEEE Std 802.3br™-2016,

and IEEE Std 802.3bz™-2016)

## **IEEE Standard for Ethernet**

Amendment 8: Physical Layer and Management Parameters for Power over Data Lines (PoDL) of Single Balanced Twisted-Pair Ethernet

Approved 7 December 2016

IEEE-SA Standards Board

ds Be COM. CITE

Abstract: Specifications and management parameters for the provision of power via a single twisted pair to connected Data Terminal Equipment (DTE) with IEEE 802.3 single balanced twistedpair interfaces are added by this amendment to IEEE Std 802.3-2015.

Keywords: 100BASE-T1, 1000BASE-T1, Ethernet, IEEE 802.3™, IEEE 802.3bu™, Power over

Acknowledgments: Portions of the material contained herein are reprinted with permission from Maxim Integrated Products, Inc., DS18B20 "Programmable Resolution 1-Wire Digital Thermometer" Data Sheet, Rev. 042208, (C) 2008. Ssion Wire Di Wire Di Scherchter Bagn 3: 2011 Cid to view the full Put of Esone Cid to view the Cid to view the full Put of Esone Cid to view the Cid to view

The Institute of Electrical and Electronics Engineers, Inc. 3 Park Avenue, New York, NY 10016-5997, USA

Copyright © 2017 by The Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Published 7 February 2017. Printed in the United States of America.

IEEE and 802 are registered trademarks in the U.S. Patent & Trademark Office, owned by The Institute of Electrical and Electronics Engineers, Incorporated.

Print: ISBN 978-1-5044-3727-1 STD22416 PDF: ISBN 978-1-5044-3728-8 STDPD22416

IEEE prohibits discrimination, harassment, and bullying.

For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

2

#### Important Notices and Disclaimers Concerning IEEE Standards Documents

IEEE documents are made available for use subject to important notices and legal disclaimers. These notices and disclaimers, or a reference to this page, appear in all standards and may be found under the heading "Important Notice" or "Important Notices and Disclaimers Concerning IEEE Standards Documents."

# Notice and Disclaimer of Liability Concerning the Use of IEEE Standards Documents

IEEE Standards documents (standards, recommended practices, and guides), both full-use and trial-use, are developed within IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Association ("IEEE-SA") Standards Board. IEEE ("the Institute") develops its standards through a consensus development process, approved by the American National Standards Institute ("ANSI"), which brings together volunteers representing varied viewpoints and interests to achieve the final product. Volunteers are not necessarily members of the Institute and participate without compensation from IEEE. While IEEE administers the process and establishes rules to promote fairness in the consensus development process, IEEE does not independently evaluate, test, or verify the accuracy of any of the information or the soundness of any judgments contained in its standards.

IEEE does not warrant or represent the accuracy or content of the material contained in its standards, and expressly disclaims all warranties (express, implied and statutory) not included in this or any other document relating to the standard, including, but not limited to, the warranties of: merchantability; fitness for a particular purpose; non-infringement; and quality accuracy, effectiveness, currency, or completeness of material. In addition, IEEE disclaims any and all conditions relating to: results; and workmanlike effort. IEEE standards documents are supplied "AS IS" and "WITH ALL FAULTS."

Use of an IEEE standard is wholly voluntary. The existence of an IEEE standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard.

In publishing and making its standards available, IEEE is not suggesting or rendering professional or other services for, or on behalf of, any person or entity nor is IEEE undertaking to perform any duty owed by any other person or entity to another. Any person utilizing any IEEE Standards document, should rely upon his or her own independent judgment in the exercise of reasonable care in any given circumstances or, as appropriate, seek the advice of a competent professional in determining the appropriateness of a given IEEE standard.

IN NO EVENT SHALL IEEE BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT LIMITED TO: PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE PUBLICATION, USE OF, OR RELIANCE UPON ANY STANDARD, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE AND REGARDLESS OF WHETHER SUCH DAMAGE WAS FORESEEABLE.

#### **Translations**

The IEEE consensus development process involves the review of documents in English only. In the event that an IEEE standard is translated, only the English version published by IEEE should be considered the approved IEEE standard.

#### Official statements

A statement, written or oral, that is not processed in accordance with the IEEE-SA Standards Board Operations Manual shall not be considered or inferred to be the official position of IEEE or any of its committees and shall not be considered to be, or be relied upon as, a formal position of IEEE. At lectures, symposia, seminars, or educational courses, an individual presenting information on IEEE standards shall make it clear that his or her views should be considered the personal views of that individual rather than the formal position of IEEE.

#### **Comments on standards**

Comments for revision of IEEE Standards documents are welcome from any interested party, regardless of membership affiliation with IEEE. However, IEEE does not provide consulting information or advice pertaining to IEEE Standards documents. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments. Since IEEE standards represent a consensus of concerned interests, it is important that any responses to comments and questions also receive the concurrence of a balance of interests. For this reason, IEEE and the members of its societies and Standards Coordinating Committees are not able to provide an instant response to comments or questions except in those cases where the matter has previously been addressed. For the same reason, IEEE does not respond to interpretation requests. Any person who would like to participate in revisions to an IEEE standard is welcome to join the relevant IEEE working group.

Comments on standards should be submitted to the following address:

Secretary, IEEE-SA Standards Board 445 Hoes Lane Piscataway, NJ 08854 USA

#### Laws and regulations

Users of IEEE Standards documents should consult all applicable laws and regulations. Compliance with the provisions of any IEEE Standards document does not imply compliance to any applicable regulatory requirements. Implementers of the standard are responsible for observing or referring to the applicable regulatory requirements. IEEE does not, by the publication of its standards, intend to urge action that is not in compliance with applicable laws, and these documents may not be construed as doing so.

## Copyrights

IEEE draft and approved standards are copyrighted by IEEE under U.S. and international copyright laws. They are made available by IEEE and are adopted for a wide variety of both public and private uses. These include both use, by reference, in laws and regulations, and use in private self-regulation, standardization, and the promotion of engineering practices and methods. By making these documents available for use and adoption by public authorities and private users, IEEE does not waive any rights in copyright to the documents.

#### **Photocopies**

Subject to payment of the appropriate fee, IEEE will grant users a limited, non-exclusive license to photocopy portions of any individual standard for company or organizational internal use or individual, non-71Amd 8:2018 commercial use only. To arrange for payment of licensing fees, please contact Copyright Clearance Center, Customer Service, 222 Rosewood Drive, Danvers, MA 01923 USA; +1 978 750 8400. Permission to photocopy portions of any individual standard for educational classroom use can also be obtained through the Copyright Clearance Center.

#### **Updating of IEEE Standards documents**

Users of IEEE Standards documents should be aware that these documents may be superseded at any time by the issuance of new editions or may be amended from time to time through the issuance of amendments, corrigenda, or errata. An official IEEE document at any point in time consists of the current edition of the document together with any amendments, corrigenda, or errata then in effect.

Every IEEE standard is subjected to review at least every ten years. When a document is more than ten years old and has not undergone a revision process, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE standard.

In order to determine whether a given document is the current edition and whether it has been amended through the issuance of amendments, corrigenda, or errata, visit the IEEE-SA Website at http:// standards ieee.org or contact IEEE at the address listed previously. For more information about the IEEE-SA or IEEE's standards development process, visit the IEEE SA Website at <a href="http://standards.ieee.org">http://standards.ieee.org</a>.

#### **Errata**

Errata, if any, for all IEEE standards can be accessed on the IEEE-SA Website at the following URL: http:// standards.ieee.org/findstds/errata/index.html. Users are encouraged to check this URL for errata periodically.

#### **Patents**

Attention is called to the possibility that implementation of this standard may require use of subject matter covered by patent rights. By publication of this standard, no position is taken by the IEEE with respect to the existence or validity of any patent rights in connection therewith. If a patent holder or patent applicant has filed a statement of assurance via an Accepted Letter of Assurance, then the statement is listed on the IEEE-SA Website at http://standards.ieee.org/about/sasb/patcom/patents.html. Letters of Assurance may indicate whether the Submitter is willing or unwilling to grant licenses under patent rights without compensation or under reasonable rates, with reasonable terms and conditions that are demonstrably free of any unfair discrimination to applicants desiring to obtain such licenses.

Essential Patent Claims may exist for which a Letter of Assurance has not been received. The IEEE is not responsible for identifying Essential Patent Claims for which a license may be required, for conducting inquiries into the legal validity or scope of Patents Claims, or determining whether any licensing terms or conditions provided in connection with submission of a Letter of Assurance, if any, or in any licensing agreements are reasonable or non-discriminatory. Users of this standard are expressly advised that determination of the validity of any patent rights, and the risk of infringement of such rights, is entirely their own responsibility. Further information may be obtained from the IEEE Standards Association.

#### **Participants**

The following individuals were officers and members of the IEEE 802.3 Working Group at the beginning of the IEEE P802.3bu Working Group ballot. Individuals may have not voted, voted for approval, disapproval, or abstained on this amendment.

David J. Law, IEEE 802.3 Working Group Chair Adam Healey, IEEE 802.3 Working Group Vice-Chair Pete Anslow, IEEE 802.3 Working Group Secretary Steven B. Carlson, IEEE 802.3 Working Group Executive Secretary Valerie Maguire, IEEE 802.3 Working Group Treasurer

Dave Dwelley, IEEE P802.3bu Power over Data Lines Task Force Chair, Phase 1

Dan Dove, IEEE P802.3bu Power over Data Lines Task Force Chair, Phase 2

Andy Gardner, IEEE P802.3bu Power over Data Lines Task Force Editor-in-Chief

Craig Chabot, IEEE P802.3bu Power over Data Lines Task Force PICS Editor

rid Abramson

Curtis Donahue

Scott Ripp

David Abramson Shadi Abughazaleh Dale Amason J. Michael Andrewartha Eric Baden Amrik Bains Thananya Baldwin Denis Beaudoin Christian Beia Michael Bennett Vipul Bhatt William Bliss **Brad Booth** Martin Bouda Ralf-Peter Braun Theodore Brillhart Paul Brooks Matthew Brown Jairo Bustos Heredia Adrian Butter Juan-Carlos Calderon J. Martin Carroll Clark Carty Geoffrey Chacon Simon Mandeep Chadha David Chalupsky Jacky Chang Xin Chang Ahmad Chini

J. Martin Carroll

Clark Carty

Geoffrey Chacon Simo

Mandeep Chadha

David Chalusky

Jacky Chang

Xin Chang

Ahmad Chini

Keng Hua Chuang

Peter Cibula

Christopher R. Cole

Shaoan Dai

John D'Ambrosia

Yair Darshan

Piers Dawe

Wael Diab

Eric DiBiaso

Daniel Dillow

Chris Diminico

Thuyen Dinh

Curtis Donahue Mike Dudek Nick Duer Frank Effenberger Hesham Elbakoury David Estes John Ewen Ramin Farjad Shahar Feldman German Feyh Alan Flatman Matthias Fritsche Richard Frosch Ali Ghiasi Joel Goergen Steven Gorshe James Graba Robert Grow Mark Gustlin Marek Hajduczenia Bernie Hammond Takehiro Hayashi Yasuo Hidaka Brian Holden Rita Horner Bernd Horrmeyer Victor Hou Yasuhiro Hyakutake Hideki Isono

Kenneth Jackson

Andrew Jimenez

Chad Jones

Peter Jones

Manabu Kagami

Upen Kareti

Keisuke Kawahara

Yasuaki Kawatsu

Michael Kelsen

Yong Kim

Jonathan King

Tom Issenhuth

Michael Klempa 8higeru Kobayashi Keisuke Kojima Paul Kolesar Tom Kolze Glen Kramer Hans Lackner Jeffrey Lapak Mark Laubach David Lewis Jon Lewis William Lo Miklos Lukacs Kent Lusted Jeffery Maki David Malicoat James Malkemus Yonatan Malkiman Arthur Marris Takeo Masuda Kirsten Matheus Erdem Matoglu Laurence Matola Brett McClellan Thomas McDermott John McDonough Richard Mei Richard Mellitz Brvan Moffitt

Leo Montreuil

Paul Mooney

Dale Murray

Henry Muyshondt

Edward Nakamoto

Gary Nicholl

Paul Nikolich

Kevin Noll

Mark Nowell

David Ofelt

Tom Palkert

Ardeshir Mohammadian

6

#### ISO/IEC/IEEE 8802-3:2017/Amd.8:2018(E)

Hui Pan Sesha Panguluri Carlos Pardo Petar Pepeljugoski Gerald Pepper Ruben Perez-Aranda Michael Peters Rick Pimpinella William Powell Richard Prodan Rick Rabinovich Adee Ran Alon Regev Duane Remein Victor Renteria Martin Rossbach Christopher Roth Salvatore Rotolo Vineet Salunke Sam Sambasivan **Edward Savre** Dieter Schicketanz Fred Schindler Peter Scruton Hossein Sedarat

Naoshi Serizawa Megha Shanbhag Stephen Shellhammer Ramin Shirani Tom Skaar Jeff Slavick Scott Sommers Tom Souvignier Edward Sprague Peter Stassar Robert Stone Junqing Sun Steve Swanson Andre Szczepanek William Szeto Bharat Tailor Akio Tajima Takayuki Tajima Satoshi Takahashi Kohichi Tamura Alexander Tan Mehmet Tazebay

Stephen Trowbridge Yoshihiro Tsukamoto Mike Tu Sterling A. Vaden Stefano Valle Paul Vanderlaan Robert Wagner Roy Wang Xinyuan Wang Matthias Wendt Oded Wertheim Martin White Natalie Wienckowsk Ludwig Winkel Peter Wu Yu Xu Jun Yi-Lennart Yseboodt Ting-Fa Yu Hayato Yuki Andrew Zambell Yan Zhuang

George Zimmerman

Helge Zinner

Albert Tretter

The following members of the individual balloting committee voted on this standard. Balloters may have voted for approval, disapproval, or abstention.

Geoffrey Thompson

Pirooz Tooyserkani

Brian Teipen

David Abramson Shadi Abughazaleh Iwan Adhicandra Thomas Alexander Dale Amason Pete Anslow Stefan Aust Amrik Bains Charles Barest Christian Boiger Ralf-Peter Braun Nancy Bravin Jairo Bustos Heredia William Byrd Steven B. Carlson Juan Carreon Mandeep Chadha Keith Chow Keng Hua Chuang Charles Cook Rodney Cummings Daniel Dove Sourav Dutta Richard Edgar German Feyh Norman Finn Matthias Fritsche Yukihiro Fujimoto Andy Gardner Devon Gayle James Gilb

Craig Gunther Marco Hernandez Guido Hiertz Werner Hoelzl Rita Horner Noriyuki Ikeuchi Osamu Ishida Atsushi Ito Raj Jain Piotr Karocki Stuart Kerry Yongbum Kim Bruce Kraemer David J. Law Jon Lewis Arthur H. Light William Lumpkins Elvis Maculuba Jeffery Maki Arthur Marris Michael Maytum Edward McCall Mick McCarthy Brett McClellan Thomas Mcdermott Richard Mellitz Tremont Miao Jeffrey Moore Charles Moorwood Rick Murphy Michael Newman Nick S. A. Nikjoo Paul Nikolich

Satoshi Obara Bansi Patel Arumugam Paventhan Ruben Perez-Aranda Michael Peters Rick Pimpinella Alon Regev Maximilian Riegel Robert Robinson Benjamin Rolfe Dan Romascanu Frank Schewe Dieter Schicketanz Stefan Schneele Thomas Starai David Stover Walter Struppler Mitsutoshi Sugawara Junqing Sun Geoffrey Thompson Mark-Rene Uchida Sterling Vaden Paul Vanderlaan George Vlantis Stephen Webb Ludwig Winkel Dayin Xu Oren Yuen

Zhen Zhou

George Zimmerman

7 Copyright © 2017 IEEE. All rights reserved.

Joel Goergen Randall Groves When the IEEE-SA Standards Board approved this standard on 7 December 2016, it had the following membership:

> Jean-Philippe Faure, Chair Ted Burse, Vice Chair John D. Kulick, Past Chair Konstantinos Karachalios, Secretary

Copyright © 2017 IEEE. All rights reserved.

#### Introduction

This introduction is not part of IEEE Std 802.3bu-2016, IEEE Standard for Ethernet—Amendment 8: Physical Layer and Management Parameters for Power over Data Lines (PoDL) of Single Balanced Twisted-Pair Ethernet.

IEEE Std 802.3<sup>TM</sup> was first published in 1985. Since the initial publication, many projects have added functionality or provided maintenance updates to the specifications and text included in the standard. Each IEEE 802.3 project/amendment is identified with a suffix (e.g., IEEE Std 802.3ba<sup>TM</sup>-2010).

The half duplex Media Access Control (MAC) protocol specified in IEEE Std 802.3-1985 is Carrier Sense Multiple Access with Collision Detection (CSMA/CD). This MAC protocol was key to the experimental Ethernet developed at Xerox Palo Alto Research Center, which had a 2.94 Mb/s data rate. Hethernet at 10 Mb/s was jointly released as a public specification by Digital Equipment Corporation (DEC), Intel and Xerox in 1980. Ethernet at 10 Mb/s was approved as an IEEE standard by the IEEE Standards Board in 1983 and subsequently published in 1985 as IEEE Std 802.3-1985. Since 1985, new media options, new speeds of operation, and new capabilities have been added to IEEE Std 802.3. A full duplex MAC protocol was added in 1997.

Some of the major additions to IEEE Std 802.3 are identified in the marketplace with their project number. This is most common for projects adding higher speeds of operation or new protocols. For example, IEEE Std 802.3u<sup>™</sup> added 100 Mb/s operation (also called Fast Ethernet), IEEE Std 802.3z added 1000 Mb/s operation (also called Gigabit Ethernet), IEEE Std 802.3ae added 10 Gb/s operation (also called 10 Gigabit Ethernet), IEEE Std 802.3ah<sup>™</sup> specified access network Ethernet (also called Ethernet in the First Mile) and IEEE Std 802.3ba added 40 Gb/s operation (also called 40 Gigabit Ethernet) and 100 Gb/s operation (also called 100 Gigabit Ethernet). These major additions are all now included in and are superseded by IEEE Std 802.3-2015 and are not maintained as separate documents.

At the date of IEEE Std 802.3bu-2016 publication, IEEE Std 802.3 is composed of the following documents:

IEEE Std 802.3-2015

Section One—Includes Clause 1 through Clause 20 and Annex A through Annex H and Annex 4A. Section One includes the specifications for 10 Mb/s operation and the MAC, frame formats and service interfaces used for all speeds of operation.

Section Two Includes Clause 21 through Clause 33 and Annex 22A through Annex 33E. Section Two includes management attributes for multiple protocols and speed of operation as well as specifications for providing power over twisted pair cabling for multiple operational speeds. It also includes general information on 100 Mb/s operation as well as most of the 100 Mb/s Physical Layer specifications.

Section Three—Includes Clause 34 through Clause 43 and Annex 36A through Annex 43C. Section Three includes general information on 1000 Mb/s operation as well as most of the 1000 Mb/s Physical Layer specifications.

Section Four—Includes Clause 44 through Clause 55 and Annex 44A through Annex 55B. Section Four includes general information on 10 Gb/s operation as well as most of the 10 Gb/s Physical Layer specifications.

Section Five—Includes Clause 56 through Clause 77 and Annex 57A through Annex 76A. Clause 56 through Clause 67 and Clause 75 through Clause 77, as well as associated annexes, specify subscriber

access and other Physical Layers and sublayers for operation from 512 kb/s to 10 Gb/s, and defines services and protocol elements that enable the exchange of IEEE Std 802.3 format frames between stations in a subscriber access network. Clause 68 specifies a 10 Gb/s Physical Layer specification. Clause 69 through Clause 74 and associated annexes specify Ethernet operation over electrical backplanes at speeds of 1000 Mb/s and 10 Gb/s.

Section Six-Includes Clause 78 through Clause 95 and Annex 83A through Annex 93C. Clause 78 specifies Energy-Efficient Ethernet. Clause 79 specifies IEEE 802.3 Organizationally Specific Link Layer Discovery Protocol (LLDP) type, length, and value (TLV) information elements. Clause 80 through Clause 95 and associated annexes includes general information on 40 Gb/s and 100 Gb/s oper ation as well the 40 Gb/s and 100 Gb/s Physical Layer specifications. Clause 90 specifies Ethernet support for time synchronization protocols.

IEEE Std 802.3bw-2015

Amendment 1—This amendment includes changes to IEEE Std 802.3-2015 and adds Clause 96. This amendment adds 100 Mb/s Physical Layer (PHY) specifications and management parameters for operation on a single balanced twisted-pair copper cable.

IEEE Std 802.3by-2016

Amendment 2—This amendment includes changes to IEEE Std 802.3-2015 and adds Clause 105 through Clause 112, Annex 109A, Annex 109B, Annex 110A, Annex 110B, and Annex 110C. This amendment adds MAC parameters, Physical Layers, and management parameters for the transfer of IEEE 802.3 format frames at 25 Gb/s.

IEEE Std 802.3bq-2016

Amendment 3—This amendment includes changes to IEEE Std 802.3-2015 and adds Clause 113 and Annex 113A. This amendment adds new Physical Layers for 25 Gb/s and 40 Gb/s operation over balanced twisted-pair structured cabling systems.

IEEE Std 802.3bp-2016

Amendment 4—This amendment includes changes to IEEE Std 802.3-2015 and adds Clause 97 and Clause 98. This amendment adds point-to-point 1 Gb/s Physical Layer (PHY) specifications and management parameters for operation on a single balanced twisted-pair copper cable in automotive and other applications not utilizing the structured wiring plant.

IEEE Std 802.3br-2016

Amendment 5—This amendment includes changes to IEEE Std 802.3-2015 and adds Clause 99. This amendment adds a MAC Merge sublayer and a MAC Merge Service Interface to support for Interspersing Express Traffic over a single link.

.press Traffic

EEE Std 802.3bn-2016 Amendment 6—This amendment adds the Physical Layer specifications and management parameters for symmetric and/or asymmetric operation of up to 10 Gb/s on point-to-multipoint Radio Frequency (RF) distribution plants comprising either amplified or passive coaxial media. It also extends the operation of Ethernet Passive Optical Networks (EPON) protocols, such as Multipoint Control Protocol (MPCP) and Operation Administration and Management (OAM).

Amendment 7—This amendment includes changes to IEEE Std 802.3-2015 and adds Clause 125 and Clause 126. This amendment adds new rates of 2.5 Gb/s and 5 Gb/s and new Physical Layers for operation at 2.5 Gb/s and 5 Gb/s over balanced twisted-pair structured cabling systems.

#### IEEE Std 802.3bu-2016

Amendment 8—This amendment includes changes to IEEE Std 802.3-2015 to define a methodology for the provision of power via a single twisted pair to connected Data Terminal Equipment (DTE) with IEEE 802.3 single twisted-pair interfaces.

A companion document IEEE Std 802.3.1 describes Ethernet management information base (MIB) modules for use with the Simple Network Management Protocol (SNMP). IEEE Std 802.3.1 is updated to add management capability for enhancements to IEEE Std 802.3 after approval of the enhancements

aticipated of a south of the other of the other of the other of the other othe IEEE Std 802.3 will continue to evolve. New Ethernet capabilities are anticipated to be added within the

## Contents

| 1.  | Introduction                                                                                                                                                                                                                                                             | . 16  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|     | 1.4 Definitions                                                                                                                                                                                                                                                          | 16    |

|     | 1.5 Abbreviations                                                                                                                                                                                                                                                        |       |

|     | 1.5 Addieviations                                                                                                                                                                                                                                                        | , 1 / |

| 30. | Management                                                                                                                                                                                                                                                               | . 18  |

|     | -                                                                                                                                                                                                                                                                        |       |

|     | 30.2 Managed objects                                                                                                                                                                                                                                                     | 4 /   |

|     | 30.2.2 Overview of managed objects                                                                                                                                                                                                                                       | .18   |

|     | 30.2.2.1Text description of managed objects                                                                                                                                                                                                                              | .18   |

|     | 30.2.3 Containment                                                                                                                                                                                                                                                       | . 18  |

|     | 30.2.5 Capabilities                                                                                                                                                                                                                                                      | . 20  |

|     | 30.2.5 Containment 30.2.5 Capabilities.  30.15 Layer management for Power over Data Lines (PoDL) of Single Balanced Twisted-Pair Ethernet 30.15.1 PoDL PSE managed object class 30.15.1.1 PoDL PSE attributes 30.15.1.1.1 aPoDLPSEID.                                    | 21    |

|     | TWISTED-PAIR Etnernet                                                                                                                                                                                                                                                    | . 21  |

|     | 30.15.1 PODL PSE managed object class                                                                                                                                                                                                                                    | . 21  |

|     | 30.15.1.1 PODL PSE attributes                                                                                                                                                                                                                                            | . 22  |

|     | 30.15.1.1.1 aPODLPSEID                                                                                                                                                                                                                                                   | . 22  |

|     | 30.13.1.1.2 aPoDLPSEAdministate                                                                                                                                                                                                                                          | . 22  |

|     | 30.15.1.1.3 aPoDLPSEPowerDetectionStatus                                                                                                                                                                                                                                 |       |

|     | 30.15.1.1.4 aPoDLPSEType                                                                                                                                                                                                                                                 |       |

|     | 30.15.1.1.5 aPoDLPSEDetectedPDType                                                                                                                                                                                                                                       |       |

|     | 30.15.1.1.6 aPoDLPSEDetectedPDPowerClass                                                                                                                                                                                                                                 |       |

|     | 30.15.1.1.7 aPoDLPSEInvalidSignatureCounter                                                                                                                                                                                                                              |       |

|     | 30.15.1.1.8 aPoDLPSEInvalidClassCounter                                                                                                                                                                                                                                  |       |

|     | 30.15.1.1.9 aPoDLPSERowerDeniedCounter                                                                                                                                                                                                                                   |       |

|     | 30.15.1.1.11 aPoDLPSEMaintainFullVoltageSignatureAbsentCounter                                                                                                                                                                                                           |       |

|     | 30.15.1.1.12 aPoDLPSEActualPower                                                                                                                                                                                                                                         | . 25  |

|     | 30.15.1.1.12 aPoDLPSEPowerAccuracy                                                                                                                                                                                                                                       |       |

|     | 30.15.1.1.14 aPoDLPSECumulativeEnergy                                                                                                                                                                                                                                    |       |

|     | 30.15.1.2 PoDL PSE actions                                                                                                                                                                                                                                               |       |

|     | 30.15.1.2.1 acPoDLPSEAdminControl                                                                                                                                                                                                                                        |       |

|     | 30.13,1.2.1 act oblit sexumineonito                                                                                                                                                                                                                                      | , 20  |

| 45. | Management Data Input/Output (MDIO) Interface                                                                                                                                                                                                                            | . 27  |

|     |                                                                                                                                                                                                                                                                          |       |

|     | 45.2 MDIO Interface Registers                                                                                                                                                                                                                                            |       |

|     | 45.2.7b Power Unit Registers                                                                                                                                                                                                                                             |       |

|     | 45.2.7b.1 PoDL PSE Control register (Register 13.0)                                                                                                                                                                                                                      |       |

|     | 45.2.7b.1.1 Enable power classification (13.0.1)                                                                                                                                                                                                                         |       |

|     | 45.2.7b.1.2 PSE Enable (13.0.0)                                                                                                                                                                                                                                          |       |

|     | 45.2.7b.2 PoDL PSE Status 1 register (Register 13.1)                                                                                                                                                                                                                     |       |

| c   | 45.2.7b.1.2 PSE Enable (13.0.0) 45.2.7b.2 PoDL PSE Status 1 register (Register 13.1) 45.2.7b.2.1 Power Denied (13.1.15) 45.2.7b.2.2 Valid Signature (13.1.14) 45.2.7b.2.3 Invalid Signature (13.1.13) 45.2.7b.2.4 Class Timeout (13.1.12) 45.2.7b.2.5 Overload (13.1.11) |       |

|     | 45.2.7b.2.2 Valid Signature (13.1.14)                                                                                                                                                                                                                                    |       |

| Q-V | 45.2.7b.2.3 Invalid Signature (13.1.13)                                                                                                                                                                                                                                  |       |

|     | 45.2.7b.2.4 Class Timeout (13.1.12)                                                                                                                                                                                                                                      |       |

| ,   | 45.2.7b.2.5 Overload (13.1.11)                                                                                                                                                                                                                                           |       |

|     | 45.2.7b.2.7 PSE Type (13.1.9:7)                                                                                                                                                                                                                                          |       |

|     | 45.2.7b.2.8 PD Class (13.1.6:3)                                                                                                                                                                                                                                          |       |

|     | 45.2.7b.2.9 PSE Status (13.1.2:0)                                                                                                                                                                                                                                        |       |

|     | 45.2.7b.3 PoDL PSE Status 2 register (Register 13.2)                                                                                                                                                                                                                     |       |

|     | 45.2.7b.3.1 Invalid Class (13.2.15)                                                                                                                                                                                                                                      |       |

|     | 45.2.7b.3.2 PD Type (13.2.2:0)                                                                                                                                                                                                                                           |       |

|     |                                                                                                                                                                                                                                                                          |       |

12

## ISO/IEC/IEEE 8802-3:2017/Amd.8:2018(E)

|      | 45.5 Protocol implementation conformance statement (PICS) proforma for Clause                                                                                                                                                                                                                              |      |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | MDIO interface                                                                                                                                                                                                                                                                                             |      |

|      | 45.5.3 Major capabilities/options                                                                                                                                                                                                                                                                          |      |

|      | 45.5.3.13b Power over Data Lines (PoDL) of Single Balanced Twiste                                                                                                                                                                                                                                          |      |

|      | management functions                                                                                                                                                                                                                                                                                       | 32   |

| 96.  | Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA) sublayer as                                                                                                                                                                                                                               | nd   |

| 90.  | baseband medium, type 100BASE-T1                                                                                                                                                                                                                                                                           |      |

|      | baseband medium, type 100BASE-11                                                                                                                                                                                                                                                                           |      |

|      | 96.5.4.1 Transmitter output droop                                                                                                                                                                                                                                                                          | 33   |

|      | 96.8.2.1 MDI return loss                                                                                                                                                                                                                                                                                   | 33   |

|      |                                                                                                                                                                                                                                                                                                            | VII. |

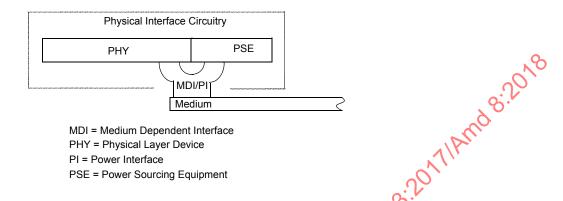

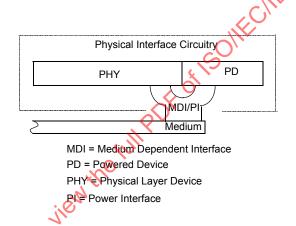

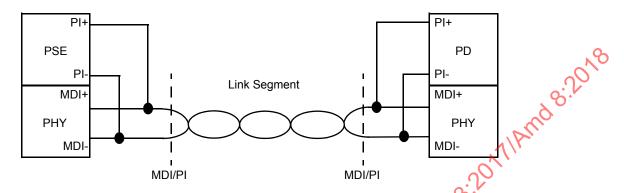

| 104. | Power over Data Lines (PoDL) of Single Balanced Twisted-Pair Ethernet                                                                                                                                                                                                                                      | 34   |

|      | Power over Data Lines (PoDL) of Single Balanced Twisted-Pair Ethernet                                                                                                                                                                                                                                      | 03.1 |

|      | 104.1 Overview                                                                                                                                                                                                                                                                                             | 34   |

|      | 104.1.1 Compatibility considerations                                                                                                                                                                                                                                                                       | 34   |

|      | 104.1.2 Relationship of PoDL to the IEEE 802.3 architecture                                                                                                                                                                                                                                                | 34   |

|      | 104.1.3 PoDL system types  104.2 Link segment                                                                                                                                                                                                                                                              | 35   |

|      | 104.2 Link segment.                                                                                                                                                                                                                                                                                        | 36   |

|      | 104.4 P. G. F. F. G. (PGE)                                                                                                                                                                                                                                                                                 | 37   |

|      | 104.4 Power Sourcing Equipment (PSE)                                                                                                                                                                                                                                                                       |      |

|      | 104.4.1 PSE types                                                                                                                                                                                                                                                                                          | 3/   |

|      | 104.4.2 PSE classes                                                                                                                                                                                                                                                                                        | 38   |

|      | 104.4.2 PSE classes 104.4.3 PSE state diagram 104.4.3.1 Overview 104.4.3.2 Conventions                                                                                                                                                                                                                     |      |

|      | 104.4.3.1 Overview                                                                                                                                                                                                                                                                                         | 38   |

|      | 104.4.3.3 Variables                                                                                                                                                                                                                                                                                        | 38   |

|      | 104.4.3.3 Variables                                                                                                                                                                                                                                                                                        | 40   |

|      | 104.4.3.5 Functions                                                                                                                                                                                                                                                                                        | 41   |

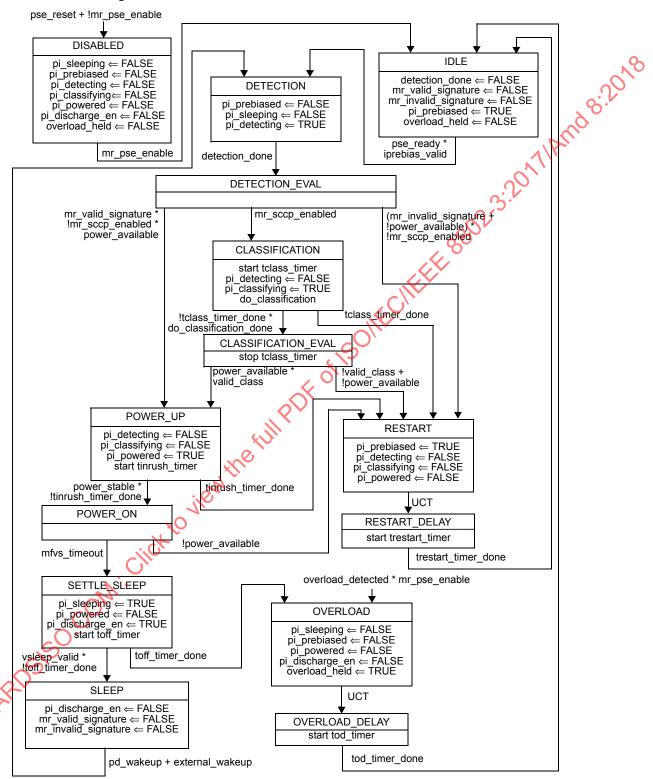

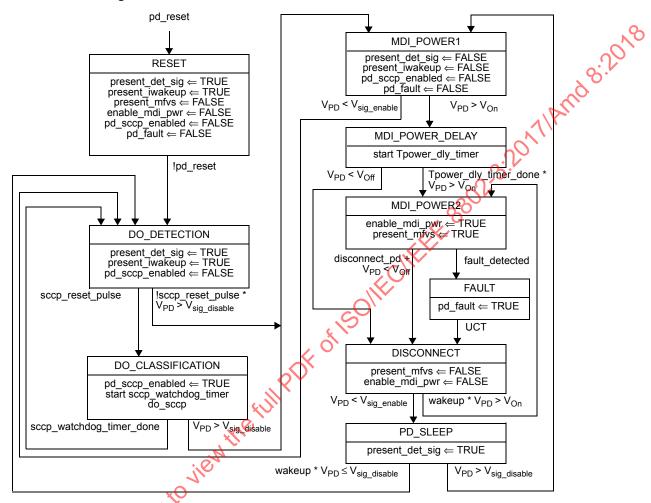

|      | 104.4.3.6 State diagram                                                                                                                                                                                                                                                                                    | 43   |

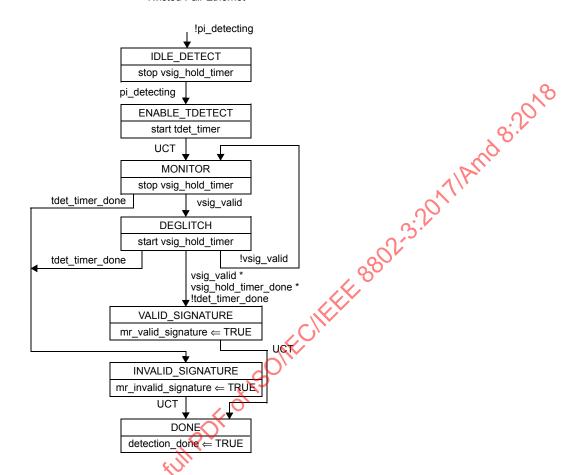

|      | 104.4.4 PSE detection of a PD                                                                                                                                                                                                                                                                              | 45   |

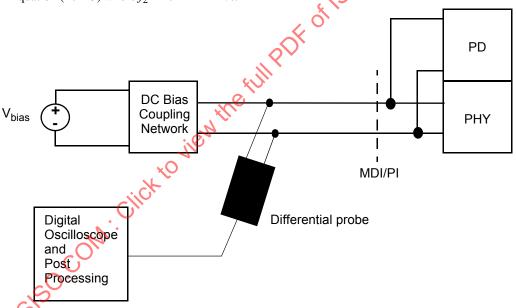

|      | 104.4.4.1 Detection probe requirements                                                                                                                                                                                                                                                                     | 45   |

|      | 104.4.4.2 Detection criteria                                                                                                                                                                                                                                                                               |      |

|      | 104.4.4.3 Rejection criteria                                                                                                                                                                                                                                                                               |      |

|      | 104.4.5 PSE classification of a PD                                                                                                                                                                                                                                                                         |      |

|      | 104.4.6 PSE output requirements                                                                                                                                                                                                                                                                            |      |

|      | 104.46.1 Output voltage                                                                                                                                                                                                                                                                                    |      |

|      | 104.4.6.2 Output current                                                                                                                                                                                                                                                                                   | 48   |

|      | 104.4.6.2.1 Output current—at overload condition                                                                                                                                                                                                                                                           |      |

|      | 104.4.6.2 Output current  104.4.6.2.1 Output current—at overload condition  104.4.6.2.2 Wakeup current signature detection  104.4.6.3 Output current requirement during idle  104.4.6.4 Inrush time  104.4.6.5 Turn off time  104.4.6.6 Disable time  104.4.6.7 Continuous output power in POWER_ON state. |      |

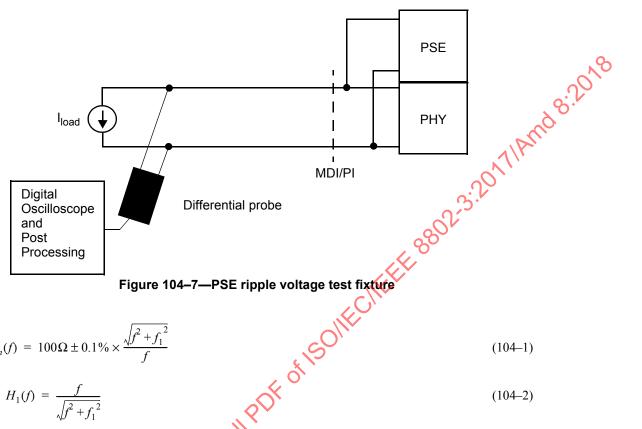

|      | 104.4.6.3 Power feeding ripple and transients                                                                                                                                                                                                                                                              |      |

|      | 104.4.6.4 Inrush time                                                                                                                                                                                                                                                                                      |      |

| Ċ    | 104.4.6.5 Turn off time                                                                                                                                                                                                                                                                                    |      |

| 20-  | 104.4.6.6 Disable time                                                                                                                                                                                                                                                                                     |      |

| Q-v  | 104.4.6.7 Continuous output power in POWER ON state                                                                                                                                                                                                                                                        |      |

|      | 104.4.7 PSE power removal                                                                                                                                                                                                                                                                                  |      |

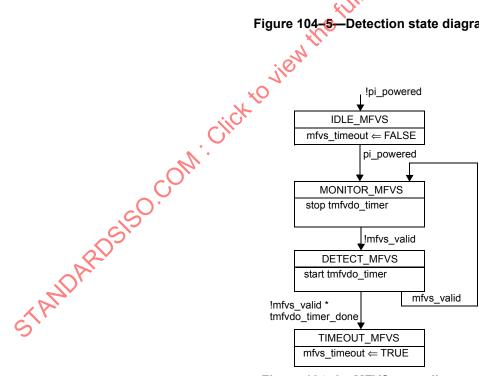

|      | 104.4.7.1 PSE MFVS requirements                                                                                                                                                                                                                                                                            |      |

|      | 104.5 Powered Device (PD)                                                                                                                                                                                                                                                                                  | 51   |

|      | 104.5.1 PD types                                                                                                                                                                                                                                                                                           |      |

|      | 104.5.2 PD classes                                                                                                                                                                                                                                                                                         |      |

|      | 104.5.3 PD state diagram                                                                                                                                                                                                                                                                                   |      |

|      | 104.5.3.1 Overview                                                                                                                                                                                                                                                                                         |      |

|      | 104 5 3 2 Conventions                                                                                                                                                                                                                                                                                      | 51   |

$\frac{13}{\text{Copyright @ 2017 IEEE. All rights reserved.}}$

## ISO/IEC/IEEE 8802-3:2017/Amd.8:2018(E)

| 104.5.3.3 Variables                                                                     | . 51 |

|-----------------------------------------------------------------------------------------|------|

| 104.5.3.4 Timers                                                                        | . 53 |

| 104.5.3.5 Functions                                                                     | . 53 |

| 104.5.3.6 State diagram                                                                 | . 54 |

| 104.5.4 PD signature                                                                    |      |

| 104.5.5 PD classification and mutual identification between the PSE and PD              |      |

| 104.5.6 PD power                                                                        |      |

| 104.5.6.1 PD discharge                                                                  |      |

| 104.5.6.2 PD input voltage                                                              |      |

| 104.5.6.3 Input current                                                                 |      |

|                                                                                         |      |

| 104.5.6.4 PD ripple and transients                                                      | 58   |

| 104 5 6 6 PD stability                                                                  | 59   |

| 104.5.6.6 PD stability                                                                  | 59   |

| 104.6 Additional electrical specifications.                                             | 50   |

| 104.6.1 Isolation                                                                       | 59   |

| 104.6.1 Isolation                                                                       | 50   |

| 104.7 Social communication classification protocol (SCCD)                               | 60   |

| 104.7 Serial communication classification protocol (SCCP)                               | . 60 |

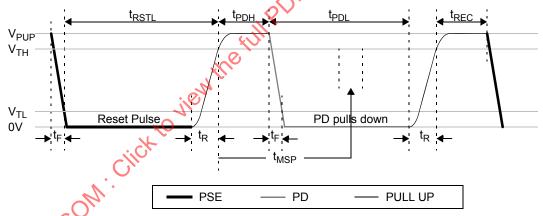

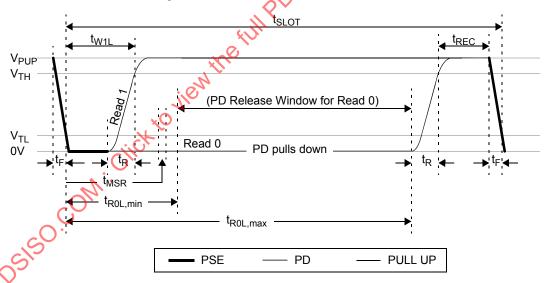

| 104.7.1.1 Initialization procedure—reset and presence pulses                            | . 00 |

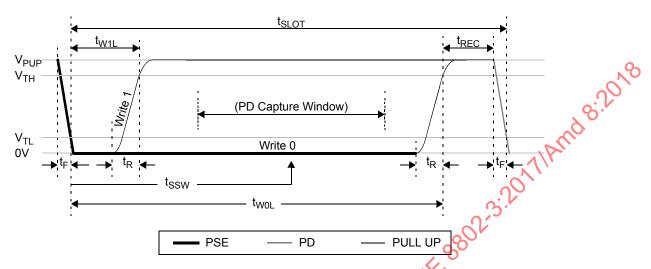

| 104.7.1.2 Write time alots                                                              | . 00 |

| 104.7.1.2 Write time slots                                                              | . 00 |

| 104.7.1.3 Read time slots                                                               | . 01 |

| 104.7.2 Serial communication classification protocols                                   | . 63 |

| 104.7.2.1 SCCP transaction sequence 104.7.2.2 Initialization 104.7.2.3 Address commands | . 63 |

| 104.7.2.2 Initialization                                                                | . 63 |

| 104.7.2.3 Address commands                                                              | . 63 |

| 104.7.2.3.1 Broadcast address [0xCC]                                                    |      |

| 104.7.2.4 Read_Scratchpad function command [0xAA]                                       | . 63 |

| 104.7.2.5 CRC8 field                                                                    | . 63 |

| 104.8 Environmental                                                                     | . 65 |

| 104.8.1 General safety                                                                  | . 65 |

| 104.8.2 Network safety.                                                                 | . 65 |

| 104.8.3 Installation and maintenance guidelines                                         |      |

| 104.8.4 Patch panel considerations.                                                     |      |

| 104.8.5 Telephony oltages                                                               |      |

| 104.8.6 Electromagnetic emissions                                                       |      |

| 104.8.7 Temperature and humidity                                                        | . 66 |

| 104.9 Protocol implementation conformance statement (PICS) proforma for Clause 104,     |      |

| Power over Data Lines (PoDL) of Single Balanced Twisted-Pair Ethernet                   |      |

| 104.91 Introduction                                                                     |      |

| 104.9.2 Identification                                                                  |      |

| 104.9.2.1 Implementation identification                                                 |      |

| 104.9.2.2 Protocol summary                                                              |      |

| 104.9.3 Major capabilities/options                                                      | . 68 |

| 104.9.4 PICS proforma tables for Clause 104, Power over Data Lines (PoDL) of            |      |

| Single Balanced Twisted-Pair Ethernet                                                   |      |

| 104.9.4.1 Link Segment                                                                  |      |

| 104.9.4.2 Power Sourcing Equipment (PSE)                                                |      |

| 104.9.4.3 Powered Device (PD)                                                           |      |

| 104.9.4.4 Common Electrical                                                             |      |

| 104.9.4.5 PSE Electrical                                                                |      |

| 104.9.4.6 PD Electrical                                                                 |      |

| 104.9.4.7 SCCP                                                                          |      |

| 104.9.4.8 Environmental                                                                 | . 76 |

14

## **IEEE Standard for Ethernet**

# Amendment 8: Physical Layer and Management Parameters for Power over Data Lines (PoDL) of Single Balanced Twisted-Pair Ethernet

NOTE—The editing instructions contained in this amendment define how to merge the material contained therein into the existing base standard and its amendments to form the comprehensive standard.<sup>1</sup>

The editing instructions are shown in **bold italic**. Four editing instructions are used: change, delete, insert, and replace. **Change** is used to make corrections in existing text or tables. The editing instruction specifies the location of the change and describes what is being changed by using strikethrough (to remove old material) and <u>underscore</u> (to add new material). **Delete** removes existing material. **Insert** adds new material without disturbing the existing material. Deletions and insertions may require renumbering. If so, renumbering instructions are given in the editing instruction. **Replace** is used to make changes in figures or equations by removing the existing figure or equation and replacing it with a new one. Editing instructions, change markings, and this NOTE will not be carried over into future editions because the changes will be incorporated into the base standard.

Cross references that refer to clauses tables, equations, or figures not covered by this amendment are high-lighted in green.

<sup>&</sup>lt;sup>1</sup>Notes in text, tables, and figures are given for information only and do not contain requirements needed to implement the standard.

Amendment 8: Physical Layer and Management Parameters for Power over Data Lines (PoDL) of Single Balanced

Twisted-Pair Ethernet

#### 1. Introduction

#### 1.4 Definitions

Insert the following definitions after 1.4.330 "Physical Signaling Sublayer (PLS)" as follows:

- **1.4.330a PoDL PD:** A Powered Device that is intended to receive power from a link section consisting of a single twisted pair. (See IEEE Std 802.3, Clause 104.)

- **1.4.330b PoDL PSE:** A device that provides power to a PoDL PD, connected via a link section consisting of a single twisted pair. DTE powering is intended to provide a single 100BASE-T1 or 1000BASE-T1 device with a unified interface for both the reception and transmission of data as well as the power to operate. (See IEEE Std 802.3, Clause 104.)

- **1.4.330c PoDL Regulated PSE:** A PoDL PSE that is required to regulate the dc voltage at the PSE MDI/PI over the required range of PD load current.

- **1.4.330d PoDL Unregulated PSE**: A PoDL PSE that is not required to regulate the voltage at the PSE MDI/PI over the required range of PD load current.

#### Change 1.4.338 as follows:

1.4.338 Power Sourcing Equipment (PSE): A DTE or midspan device that provides the power to a single link section. PSEs are defined for use with two different types of balanced twisted-pair PHYs. When used with 2 or 4 pair balanced twisted-pair (BASE-T) PHYs, (see TEEE Std 802.3, Clause 33), DTE powering is intended to provide a single 10BASE-T, 100BASE-TX, or 1000BASE-T device with a unified interface for both the data it requires and the power to process these data. When used with single balanced twisted-pair (BASE-T1) PHYs (see TEEE Std 802.3, Clause 104), DTE powering is intended to provide a single 100BASE-T1 or 1000BASE-T1 device with a unified interface for both the data it requires and the power to process these data. A PSE used with balanced single twisted-pair PHYs is also referred to as a PoDL PSE.

#### Change 1.4.415 as follows:

**1.4.415 Type 1 PD**: A PD that does not provide a Class 4 provides a Class 0, 1, 2, or 3 signature during Physical Layer classification, and that is not a PoDL PD. (See IEEE Std 802.3, Clause 33.)

Insert the following definitions after 1.4.418 "Type 2 PSE" as follows:

- **1.4.418a Type APoDL System:** A system comprising a PoDL PSE, link section, and PD that are compatible with 100BASE-T1 PHYs.

- **1.4.418b** Type B PoDL System: A system comprising a PoDL PSE, link section, and PD that are comparible with 1000BASE-T1 PHYs.

- **1.4.418c Type C PoDL System:** A PoDL PSE, link section, and PD that are compatible with both 100BASE-T1 and 1000BASE-T1 PHYs.

- **1.4.418d Type D PoDL System:** A PoDL PSE, link section, and PD that lack a data entity or are incompatible with IEEE 802.3 PHYs.

#### 1.5 Abbreviations

STANDARDSEO COM. CHICK TO VIEW THE FUIL POR OF SOME OF THE PROPERTY OF STANDARDS STAND Insert the following new abbreviations into the list, in alphabetical order:

#### 30. Management

#### Change the first paragraph of Clause 30 as follows:

This clause provides the Layer Management specification for DTEs, repeaters, MAUs, and Midspans based on the CSMA/CD access method. The clause is produced from the ISO framework additions to Clause 5, Layer Management; Clause 19, Repeater Management; and Clause 20, MAU Management. It incorporates additions to the objects, attributes, and behaviours to support 100 Mb/s, 1000 Mb/s and 10 Gb/s, full duplex operation, MAC Control, Link Aggregation, DTE Power via MDI, Power over Data Lines, subscriber access networks, and the Link Layer Discovery Protocol (LLDP) IEEE 802.3 Organizationally Specific TLVs, The objects, attributes, and behaviours to support Link Aggregation are deprecated by IEEE Std 802.1AX<sub>-2</sub>008. EEEE 8802.3.20

#### 30.2 Managed objects

#### 30.2.2 Overview of managed objects

#### 30.2.2.1 Text description of managed objects

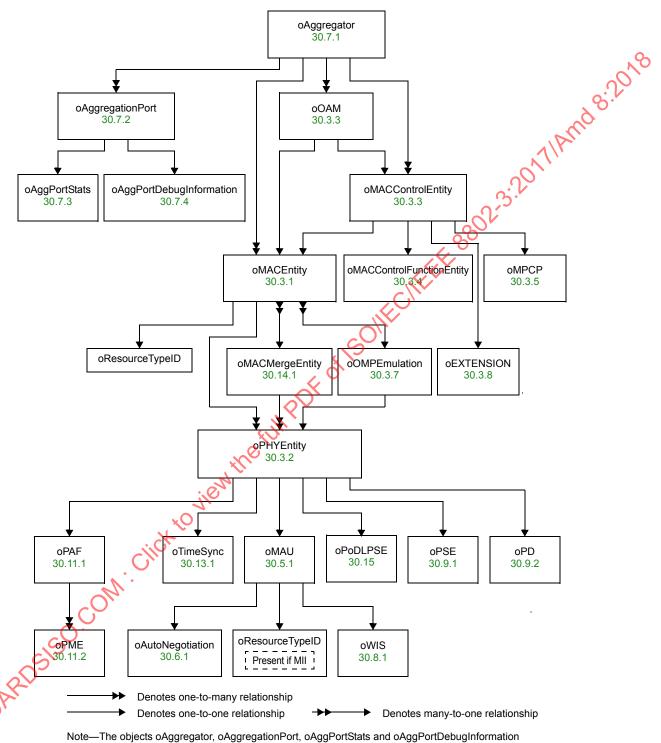

Change the entry for oPHYEntity as follows:

If oOMPEmulation is implemented, oPHYEntity is contained within oOMPEmuoPHYEntity

> lation. Otherwise oPHYEntity is contained within oMACEntity. Many instances of oPHYEntity may coexist within one instance of oMACEntity; however, only one PHY may be active for data transfer to and from the MAC at any one time. oPHYEntity is the managed object that contains the MAU, PAF, and PSE, and

<u>PoDLPSE</u> managed objects in a DTE.

Insert the following new entry for oPoDLPSE into the list, in alphabetical order:

oPoDLPSE The managed object of that portion of the containment trees shown in

Figure 30–3. The attributes, notifications, and actions defined in 30.15 are con-

tained within the PoDLPSE managed object.

#### 30.2.3 Containment

## Change the first paragraph of 30.2.3 as follows:

A containment relationship is a structuring relationship for managed objects in which the existence of a managed object is dependent on the existence of a containing managed object. The contained managed object is said to be the subordinate managed object, and the containing managed object the superior managed object. The containment relationship is used for naming managed objects. The local containment relationships among object classes are depicted in the entity relationship diagrams, Figure 30–3 through Figure 30-6. These figures show the names of the object classes and whether a particular containment relationship is one-to-one, one-to-many or many-to-one. For further requirements on this topic, see IEEE Std 802.1F-1993. PSE <u>and PoDL PSE</u> management <u>are <del>is o</del>nly valid in a system that provides management</u> at the next higher containment level, that is, either a DTE, <u>or in the case of PSE management only, a repeater</u> or Midspan with management.

#### Replace Figure 30-3 (as modified by IEEE Std 802.3br-2016) with the following:

are deprecated by IEEE Std 802.1AX-2008.

Figure 30-3— DTE System entity relationship diagram

#### 30.2.5 Capabilities

#### Change the first paragraph in 30.2.5 as follows:

This standard makes use of the concept of packages as defined in ISO/IEC 10165-4:1992 as a means of grouping behaviour, attributes, actions, and notifications within a managed object class definition. Packages may either be mandatory, or be conditional, that is to say, present if a given condition is true. Within this standard capabilities are defined, each of which corresponds to a set of packages, which are components of a number of managed object class definitions and which share the same condition for presence. Implementation of the appropriate Basic and Mandatory packages is the minimum requirement for claiming conformance to IEEE 802.3 Management. Implementation of an entire optional capability is required in order to claim conformance to that capability. The capabilities and packages for IEEE 802.3 Management are specified in Table 30–1a through Table 30–9 Table 30–10.

#### Change the ninth paragraph as follows: